Типове памет

1. Памет с произволен достъп. DRAM, SRAM.

Характерно за паметта с произволен достъп – RAM (random access memory) е, че тя има сравнително малък капацитет и голямо бързодействие.

Друга характерна особеност на тази памет е нейната енергозависимост - при отпадане на захранването информацията в нея се губи.

Всеки бит информация в оперативната памет се намира в клетка памет. При нея микропроцесорът има директен достъп до всяка клетка от паметта във всеки момент от времето.

Възможни са и се използват две техники за изграждане на тези клетки.

Едната е тази при която състоянието на клетката зависи от това какъв е електрическият заряд в нея. При другата състоянието на клетката зависи от протичането на ток.

Първата оперативна памет е феромагнитна.

1.1 Динамична памет с произволен достъп- DRAM.

Най-разпространена е динамичната памет с произволен достъп или DRAM (Dynamic RAM). Тя може да се намери практически във всички настолни и преносими компютри, но изисква електрическо захранване, за да поддържа своето съдържание. Това означава, че ако изключите компютъра или електрозахранването прекъсне, съдържанието на паметта се изтрива. Bсичко, над което сте работили до момента изчезва и цялата памет на компютъра отново е празна.

За съхранение на информацията в тази памет се използват малки кондензатори. Кондензаторът може да функционира като памет, защото зарядът върху него може да се контролира. Зарядът между плоскостите на кондензатора може да съхрани единично състояние или единичен бит цифрова информация. Тъй като изолаторът между плочите на кондензатора не е идеален, част от заряда се губи. За това е необходимо периодически зарядите в кондензаторите да се опресняват - презареждане на кондензаторите.

Поради необходимостта от опресняване такава памет се нарича динамична (dynamic memory). Интегралните схеми които осигуряват този вид памет се наричат динамичен RAM или DRAM чипове.

В паметта на РС специални полупроводникови вериги, които могат да реагират като кондензатори се използват на мястото на същинските кондензатори с метални плоскости. Голям брой от тези вериги се комбинират, за да създадат един интегрален чип динамична памет.

Опресняване ( refreshing ) на паметта се извършва през няколко ns.

Опресняването при DRAM се извършва по време на всеки read, write, RAS цикъл.

Четенето на DRAM включва разреждането на кондензатор през транзистор във външната верига (шина данни-data bus). Кондензаторът след това автоматично се презарежда до оригиналната си стойност и този процес се нарича презареждане . По време на презареждането ( Precharge delay ) процесорът няма достъп до DRAM.

Динамичната памет има висока пакетираща гъстота (RAS & CAS сигнали), бавен достъп (2,5 -100 ns) и ниска консумация на ток.

Забележка:Термини използвани при DRAM

RAS (Row Address Strobe) - входен сигнал, който избира ред от запомнящата матрица. Подава се преди сигналът CAS.

CAS (Column Address Strobe) - входен сигнал, който избира колона от запомнящата матрица.

Burst - пакетна операция на четене/запис, при която се работи с няколко последователни думи. Означение от типа 3-1-1-1 за Burst цикъла показва, че от паметта се четат 4 последователни думи. За прочитане на първата от тях са необходими 3, а за всяка от следващите по 1 тактов импулс.

Precharge - команда за дезактивиране на единия от двата блока или и двата блока на чипа. Изпълнява се при подаването на определена входна комбинация от управляващи сигнали (RAS,CAS и др.), но може да се извърши и автоматично по време на операциите за четене или запис.

CAS Latency - задава броя на тактовите импулси 1, 2 или 3, които трябва да се изчакат от подаването на команда Read до появата на валидни данни.

Пример за основна клетка при динамичните памети e показан на фигура 1.

АШ – адресна шина;

РШ – разрядна щина

Фиг.1

Тя представлява запомнящ кондензатор с капацитет С1 и последователно свързан MOS транзистор с индуциран канал. Транзисторът Т служи като ключ, позволяващ зареждането и разреждането на запомнящия кондензатор С1 при запис и четене.

Основният проблем при тази клетка е получаването на достатъчно голям сигнал при четене. Запомнящия капацитет С1 има стоиност 0,7-0,05pF, стойност много по-малка от стойността на капацитета на разрядната шина С2. Така прочетеният сигнал е много по-малък от първоначалното напрежение върху С1. Това изисква увеличаване на С1 и намаляване на С2, както и увеличаване на чувствителността на усилвателя за четене.

1.2 Статична памет с директен достъп - SRAM.

Статичната памет действа като потенциален ключ, който позволява или прекъсва потока на електричеството. Основната клетка в такава памет може да бъде тригер, който има две устойчиви състояния. Всеки тригер може да съхрани един бит двоична информация.

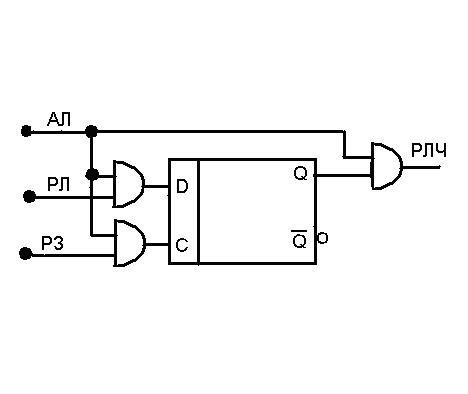

Пример за основна клетка на статична памет с директен достъп е показан на фигура 2.

Фиг.2

Тази клетка е изградена от Д тригер и три управляващи логически елемента “AND” .

АЛ - адресна линия

РЛ - разрядна линия за запис

РЗ - разрешение за запис

РЛЧ - разрядна линия за четене

За да се активира клетката за запис или четене на АЛ се подава 1. Тогава в нея може да се записва или от нея може да се чете вече записана информация. При запис информациятa / 0 или 1 / се подава на РЛ. Подава се 1 и на РЛЗ.

При четене на АЛ се подава 1, на РЗ се подава 0. Тогава съдържанието на клетката излиза на РЛЧ.

Ако предлагате частни уроци, може да рекламирате услугите си напълно безплатно!

Ако предлагате частни уроци, може да рекламирате услугите си напълно безплатно!

Коментари