32 разрядни микропроцесори.

Особености. Конвейерна обработка на инструкциите

- Особености на 32- разрядните процесори

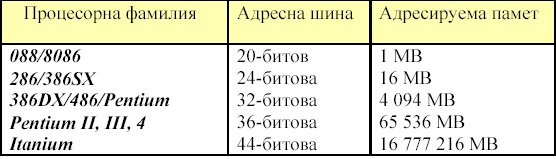

През 1985г. на 17.10. Intel анонсира първия 32-разряден микропроцесор i80386. Този МР има пълна 32-разрядна архитектура (32-разрядни регистри и 32-разрядна външна шина) и работи на тактова честота 16МHz. Става възможно да се адресира 4 GB физически и 64 ТВ виртуална памет

През 1993г. Intel обявява началото на промишленото производство на 32-разрядни МР от ново поколение, Pеntium. Този МР има 32-разрядна адресация и 64-разрядна външна шина, тактова честота 60 и 66 МНz. Нововъведение е, че 6 байтовата опашка от инструкции е заменена с двустепенен конвейер. Всички регистри освен сегментните са 32 разрядни, но за обезпечаване на съвместимост с предходните процесори от семейството на Intel 80x86 може отделно да се адресират техните младши 16 битови половини. Осемте регистъра с общо предназнаение могат да се адресират като цяло и само техните 16 младши байта. PSW е 32 разряден. Сегментните регистри са 6 и са 16 битови. 32 битов указател на команди.Микропроцесор i80386 има три режима на работа:

a) Реален – Real Address Mode – режим на реална адресация (реален режим – Real Mode), който е напълно съвместим с режима на работа на i8086. В този режим е възможна адресация до 1МВ физическа памет.

b) Защитен - Protected Virtual Address Mode – защитен режим на виртуална адресация (защитен режим – Protected Mode). В този режим процесорът може да адресира до 4GB физическа памет, чрез които с използване на странична организация може да се оперира с 64 ТВ виртуална памет за която и да е задача.

c) Виртуален .

Страничната организация на паметта е най – интересната нова възможност на i80386

За ускоряване на последователните обръщения към паметта се използва конвейер. За ускоряване на достъпа до паметта в процесора i80386 за първи път се използва кеш памет.

Пуснаха се модели на i80386, работещи на тактова честота 16, 20 (от февруари 1987 г.), 25 (от април 1988 г.) и 33 (от април 1989 г.) MHz.

За 32 битовите процесори бяха разработени операционни системи Microsoft Windows NT и Microsoft Windows 95 (по късно известна като «Chicago»).Всяка от двете операционни системи е многозадачна

На основата на i80386 фирмата IBM създаде IBM AT 386 от семейството на РС и IBM PS/2-8- от семейството на PS/2. Първата използваше операционна система PC-DOS, а втората OS/2.

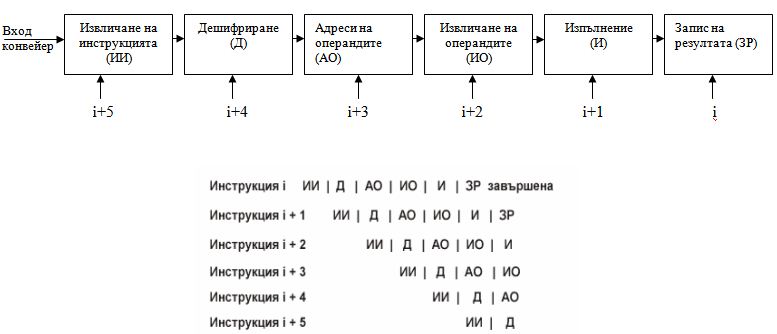

1. Конвейерна обработка на инструкциите При 32-битовите микропроцесори са въведени вътрешни конвейери за изпълнение на инструкциите, което им позволява да изпълняват няколко инструкции едновременно. Тази технология осигурява допълнителна производителност спрямо по-ранните поколения компютърни системи. Конвейерната архитектура обикновено се свързва с високопроизводителните RISC (Reduced Instruction Set Code)процесори. RISC процесорите имат опростен набор инструкции, които освен че са по-прости, са и по-малко на брой. Въпреки че всяка инструкция върши по-малко работа, като цяло тактовата честота може да бъде по-висока, което увеличава производителността. Целта е всяка инструкция да се изпълнява за един машинен цикъл при възможност за паралелно изпълнение на инструкциите. Следствие на RISC процесорите са суперскаларните процесори. Те изпълняват няколко целочислени инструкции за един машинен цикъл. Обикновено CISC ( Complex Instruction Set Code)процесорите използват по-богат и по-пълен набор от инструкции. Някои от тези инструкции са доста сложни. За изпълнението им се налага те да бъдат разделени на няколко по-прости операции(микрооперации). Например, една операция за сумиране на две числа (данни), намиращи се в паметта, изисква да се изпълнят няколко по-прости операции: a) извличане (прочитане) на инструкцията от паметта, b) декодиране (дешифриране) на командата, формиране на адресите на данните, които се обработват, c) извличане на данните (операндите) от паметта и записването им в регистрите, изпълнение на операцията (сумиране), d) записване на резултата в паметта и т.н. Тези прости операции общо взето съответстват на набора операции, характерни за RISC процесорите. Както се вижда, разликата между RISC и CISC процесорите се състои в това, че CISC процесорите имат вътрешно машинно реализирани по сложни команди, които обаче са съставени от по-прости (RISC) инструкции. Допуска се инструкциите да се изпълняват за повече от един машинен цикъл. При CISC процесорите отделните етапи от изпълнението на една сложна команда се изпълняват от отделни, независими електронни устройства. Това позволява подреждането на тези устройства в конвейерна верига за последователно изпълнение на инструкциите. Терминът е заимстван от машиностроителната индустрия и описва сходна структура, както конвейера в типичните машиностроителни производства. В определен момент дадена инструкция се обработва в някое от устройствата на конвейера и след това преминава в следващото. Устройствата през които е преминала дадена инструкция не са натоварени до края на изпълнение на командата и би трябвало да престояват през този период от време. За да не се получава това, тези устройства могат да започнат изпълнение на следващата команда паралелно с изпълнението на текущата. Така се получава застъпване на отделните етапи в изпълнението на няколко операции, което реализира конвейерна организация в работата на устройствата на микропроцесора (фиг.4.3). a) Извличане на инструкцията (ИИ) b) Дешифриране (Д) c) Адреси на операндите (АО) d) Извличане на операндите (ИО) e) Изпълнение (И) f) Запис на резултата (ЗР) Конвейерна обработка на инструкциите

В даден момент от време всяко устройство обработва различна команда, която се намира в различна степен на завършеност. Когато една инструкция влиза в конвейера, друга излиза, а още няколко се намират в конвейера на различен етап от изпълнението й. Броят на устройствата в конвейера е различен за различните микропроцесори. Понякога броя на устройствата в конвейера се нарича ширина на конвейера Ако се приеме, че броя на устройствата в конвейера е n, то би трябвало производителността на микропроцесора да се увеличи n пъти в сравнение с безконвейерния микропроцесор. Това е така само в случаите:

- когато програмата не съдържа инструкции за преход (инструкцията която следва зависи от резултата на текущата инструкция) ;

- когато отделните инструкции са с еднакво времетраене;

- всички операции минават през всички устройства.

На практика тези условия трудно се изпълняват за цялата програма, поради което производителността е по-ниска от теоретичната.

Микропроцесорите при които за първи път се използва тази технология (80386) има 6 степенна конвейерна организация. В съвременните микропроцесорни системи (от типа Pentium) се използват по няколко конвейерни вериги. Intel наричат възможността за

изпълнение на инструкциите в повече от една конвейерна верига суперскаларна

DEC X - намаляване на съдържанието на регистър Х с единица(1)

LD X A – зарежда регистър А от адрес записан в Х

ADD A X – събира съдържанието на А и Х

С конвейер – 9 машинни цикъла

Без конвейер – 11 машинни цикъла

Ако предлагате частни уроци, може да рекламирате услугите си напълно безплатно!

Ако предлагате частни уроци, може да рекламирате услугите си напълно безплатно!

Коментари